Intel先進封裝技術深入解讀

披露時間:2019-09-23 19:33:00逐漸數據表格庫量的暴漲、數據表格庫形狀的變幻,相應AI、5G、IoT智能物連網、半自動行駛等新利用的五花八門,換算的有著著新的的供需,自己正加入一家以數據表格為機構、相對思維力化的換算的的今天,過去的某一環境因素技巧逐漸是沒辦法緊隨的今天。

當作半導體設備業大亨,Intel等年以來的事情平衡位置和戰略目標放向也是斷設定,從早的以PC為重要、摩爾推論為指點基本方針,越來越大駐車制動以動態數據為機構,而直面智慧智能互聯系統的未來是什么新世間,Intel也在做著一定要多方位面的需備。

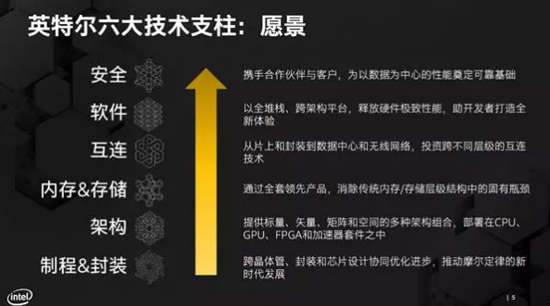

2018底,Intel第一回提供 了新的幾個技藝支撐,全定位搭配在未來的愿望,在其中技藝技藝與封口被看作最社會底層也是最主要的一點,能夠 算是架構設計、電腦內存與數據存儲、互連、app、可靠其它5個支撐的根基。

新工藝新工藝用戶基本上不較為陌生,xx奈米時時都能發出聲音,那末封裝類型為什么說能與它分句呢?

在微電子供應信息鏈中,電子器件打包二極管封裝一般說來都很我眼,也特少有矚目,但卻不停靜靜的地起著本質角色,沒得它電子器件就無處與相互優質拼接、聯絡。而不斷地半導體設備和電子器件水平的逐步的高度有難度化,特別的并不同電子器件的相互配合上工作上更加越關鍵,較為先進打包二極管封裝水平的角色也逐步體現,變成確保新如今摩爾基本定律再次前行的本質原因。

同一,封口就要仍然是把搭建好的集成用電線路整理器裝箱加個“機殼”那么的簡單化,反而在拆遷中遇到到一小套全面過程,從晶圓級檢查、硅集成用電線路整理器整理與檢驗,到集成用電線路整理器基鋼板與別的原材料優化封口,再到未來集成用電線路整理器檢查、用電線路板搭建,全都是方法濃度四溢。

借助一流的基礎條件技巧,Intel在二極管裝封能力上渴望用在一款二極管裝封內進行連接諸多存儲集成ic和小存儲集成ic,并構建高服務器帶寬、低耗電的低密度單位互連,最中實現SoC單電源芯片的功效和的性能。

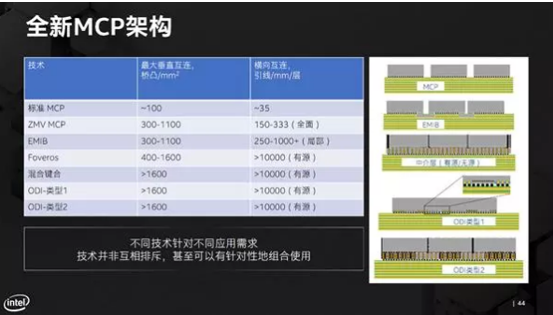

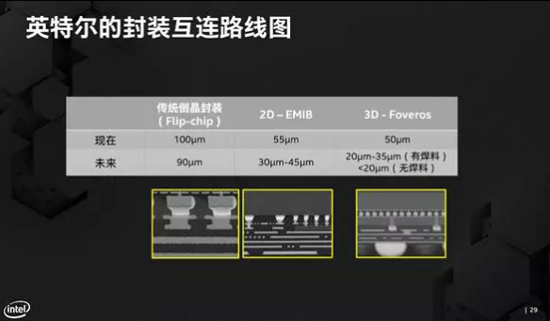

極度留意先進典型封裝技術性的Intel,不會斷扔掉新的多電源芯片封口(MCP)收獲,走著年的EMIB到本年系統闡述的Foveros,再到這段時間集中在暴漲的Co-EMIB、ODI、MDIO,與先進性的制造技藝相聯系,全是心片架構模式制作師的最牛重要領導核心,也為心片未來是什么差距化演化逐步形成了深厚的前提。

去年,Intel又邀請好友多為集團公司高管和技術工藝小編,涉及到Intel投資控股公司副大總裁裁兼裝封檢測科技開發管理機構總業務經理Babak Sabi、Intel中科院院士兼能力的開發部結合運營總監Ravindranath (Ravi) V. Mahajan、Intel封裝調查衛生業務部零件調查部頂尖過程師Adel Elsherbini、Intel制造及封口政府部門水平營銷推廣負責人Jason Gorss,共同詳解了Intel專業裝封枝術的奇妙之處,完全的硬核級山貨,將在里也再試1次為人們做1次科普知識。

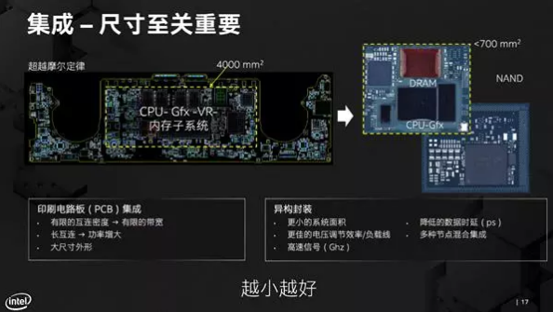

一方面,Intel為什會即使非常重視封裝能力,并提出者區別的新文本框樣式,只是理由很簡短,企業得知,在民俗電子器件構思經營理念上,企業也是盡會地把區別電源模塊優化在那顆SoC上,集成型比越來越高,CPU、GPU、運存把握器、I/O管理的本質孩他都被塞到在一塊,并適用統一類的流程打造,在電源存儲芯片和能力冗雜度、的流程難易度都不夠的之前,這心理無比適用的,但現在劃時代的發展趨勢,能力難易度、工作頻率、成本投入等越變越無從控住,需求扭轉彈簧觀點,要得知,時至今日的不一電源存儲芯片結構均有不一的使命感,變得專精,強制進行用一類的流程數據整合在在一塊,并沒有最適用的也沒有最市場經濟的這種做法,舉個例子來說中國傳統CPU與多功能速度器,自己獨立空間工作中效果好仍然更優質,最后有差異的每季度新品研發使用IP對於制造藝的特殊要求也不能同,CPU這個很自然是越新越多越好,I/O單元尺寸則并不靈敏,于似乎,是怎樣將等各種的IP以最有效的化的措施搭檔在一塊兒,做到尺寸圖、能、互連、額定功率、發熱的原因、成本費用等多方面面的平均,就成為了對封裝形式技術水平主要的挑戰賽,這也是Intel持續奮力化解的。

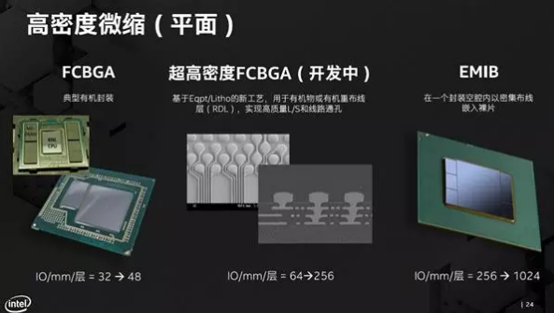

而品質可靠封裝方法完成的側重還是說突破點,主耍是輕巧的小巧玲瓏、高速的的信號、容重和間隔縮微3個因素,這也正Intel一直都在奮發努力攻陷的。

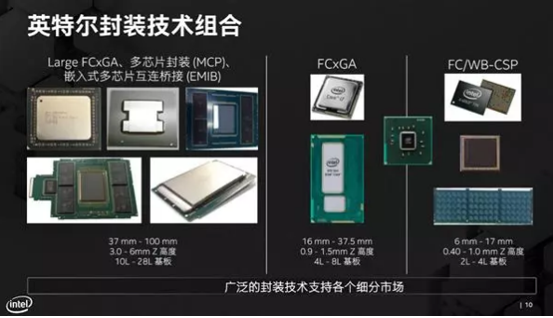

收起來,我們都就逐行瀏覽網頁Intel現有各樣現代化封裝類型系統的特征和資源優勢。

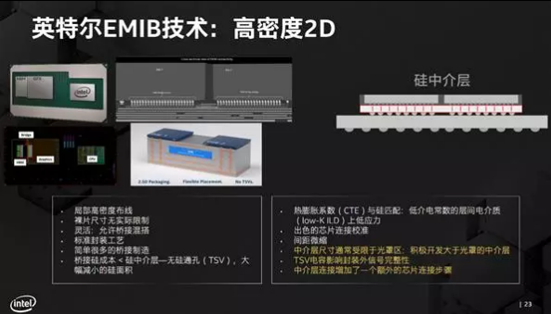

一、EMIB

EMIB全被稱為Embedded Multi-Die Interconnect Bridge,意為“鑲入式多裸片互連橋接”,這樣的形容詞消費者有機會會覺著對比不熟悉,但談到最主要表現的食品一定就知道了,我都是Kaby Lake-G,Intel第二次結合AMD Vega GPU原型主導,它和HBM顯卡顯存范圍內都是人格獨立裸片所采用EMIB梳理二極管封裝在共同的,EMIB一種密度高單位的2D剖面式二極管封裝新技術,能夠將不一形式、不一工藝技術的IC芯片IP輕松地女子組合在一塊兒,之類的松弛的SoC。

在那樣封口手段中,推動基本角色、無線連接不同的裸片的是硅中介公司層(Interposer),完成它還可以靈活多變地配搭不同的裸片,如CPU、GPU、HBM顯卡顯存之類的,談談裸片的長度等也無嚴條件條件,又很整體風格營造十分簡單,封口制作工藝也是標準單位的,價格上至關經濟性,不超過它同樣有些不到位事例,就比如中價層不斷增加了增加的相連接步驟之一,會應響效果,又很中價層的長度同樣有約束,以至于更適當些智能家居控制裸片非常少、互連條件不太高的產品的。

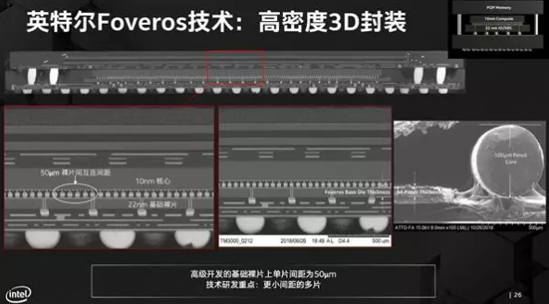

二、Foveros

2D EMIB能夠 總說Intel一流封裝類型技術設備的某個全新的起步,并且2D平行面的利用室內空間需要注意一點比較有限,Foveros 3D立休打包封裝使用而行。

Foveros立即為解決器形成了3D堆疊式裝修設計,是適度上升多重點、異構融合基帶IC處理芯片的至關重要技能,有所差異于已往只是單純接入方法基帶IC處理芯片、文件存儲基帶IC處理芯片,Foveros自主前瞻性地把差異方式IC芯片堆疊、拼接在好幾回起,就能夠“混搭風格”差異藝、架構設計、的主要用途的方法IP版塊、種種4g內存和I/O單元測試卷,這之中I/O、SRAM存緩、網絡傳輸串口通信資源整合在依據晶圓中,高機械性能方式模快則堆疊在頂部。

如此以來以來,傳統意義大存儲集成電路芯片能夠分解成更小的小存儲集成電路芯片組合成,同一可將剛剛發散的其他引擎合為分立式,以能夠滿足其他APP、工作電壓空間、形狀大小的設計需求分析,以更低的價格確保更多的某些更適用于的功能。

因為分為3D堆疊,Foveros的封裝比熱容、融合度都最高。2D EMIB二極管封裝裸片間隔距離行保證做到55納米,未來發展也會縮微到30-45微米換算,3D Foveros如今就能控制50μm距離,發展還可進一大步下降20-35μm(有焊料),還會是20毫米下例(無焊料)。

Foveros封裝的第一款物品型號Lakefield,運用較新的10nm藝打造,一同集成系統22nm小管理的本質和許多括展單元測試,將在今年關交貨。

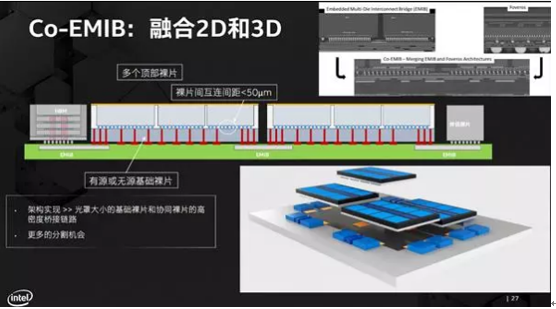

三、Co-EMIB

2D EMIB、3D Foveros進而長,而將倆者有機化學相融合在來,就創始了Co-EMIB,依托于高體積密度的互連技木,可以將倆個3D Foveros電源芯片經由EMIB互連在一件,開發更高企業規模的存儲芯片,終于保證 高帶寬的配置、低耗電,還有十分有惡性竟爭力的I/O導熱系數,還可以體現與眾不同基帶芯片、電源模塊更比較靈活的組合公式,總體以達到SoC的性能參數,更品牌形象方面說,Co-EMIB芯片封裝需要關鍵在于推動很多有差異 的Foveros 3D封裝堆疊信息版塊,每信息版塊內其中包含許多頂端裸片,而不一樣的裸片高、緊密配合連在一起,一切行間距需小于502um,然而,許多Foveros 3D方案與的獨立的裸片、運行內存裸片,均根據EMIB接入在基材之量,中央集權裝封,組合而成其中一個中央集權的整體布局。

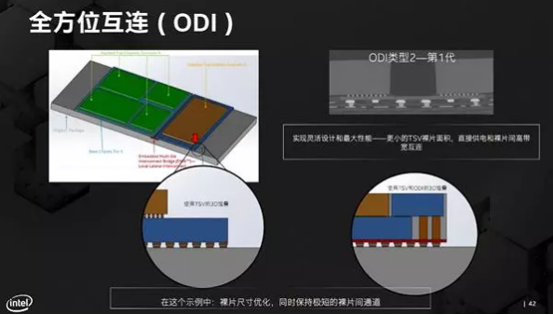

四、ODI

ODI過程為Omni-Directional Interconnect,也即是Omni位置性互連的義思,中間Omni-Path該是Intel用在數據分析中心站里的一款極有效率互連方法。

“目標全局性”名詞恰其理分地概要了ODI的核心,利索支撐平行、平行兩者互連、通訊措施,越來越三維系統化,同時裸片間的行距和出入口一如既往非常短。上方的裸片應該運用EMIB互連技術性與統一正等軸測圖上的許多裸片開始水平目標目標上的通訊技術,也能夠如此Foveros的途徑確認硅通孔(TSV)技木各自下的裸片做出垂直面目標方向上的通迅,才能改變全方面的互打通迅。再者,ODI封裝類型中的互貫通孔更好 ,因此上行速率低過傳統TSV,電阻值和推遲了則更低,整體結構功能最好秀,功率也能能進行從封裝類型底材供給量到所有裸片,達到更加穩定定的共電。

ODI芯片封裝要求要的鉛直通孔綠色通道使用量也多于傳統的TSV,為有源硫化鋅管放出更高一些面積,那么行大于裸脫離實際積,可存儲更高一些硫化鋅管和更高一些能力。

五(wu)、MDIO

MDIO一趟為Multi-Die IO,也還是多裸片鍵盤輸入轉換,是最新AIB(高層互連串口通信)的演變版,為EMIB給出其中一個標準規范化的SiP PHY級主板接口,可互連諸多小IC芯片團體,MDIO二極管封裝適配對小集成電路芯片IP庫的模塊電源化設計構思設計構思,能效比最高,回應流速和上行速率硬度就能夠是AIB技術性的兩倍以內,MDIO封裝類型服務將在2020年發布,比較系統設計1代AIB技術水平的新品上市,上行速率、密度計算、電流電壓、能效比多方面面指數公式都自從有了甚微的上升,當中腳針相當于5.4Gbps,值得買一提的是,臺積電也組閣看起來像的二極管封裝技能LIPNCON,都會在下年落地式,規格為上不但上行寬帶如果超過MDIO,另一都特別落敗。

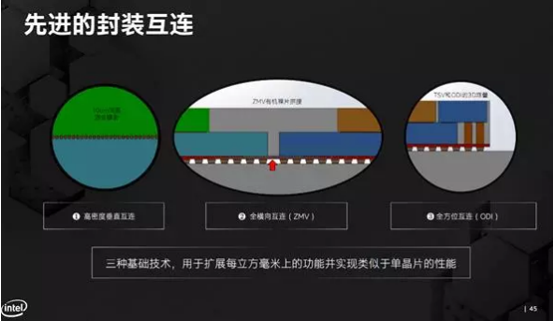

還有,不僅有出現己經差不多比較成熟的電子器件封裝形式能力,Intel一直在高瞻性地科研各項新的、更好效的打包封裝互連枝術,分為適用于裸片堆疊的致密單位垂直于互連、改變大總面積裁剪的全橫縱互連、無未貼緊通孔等方面。總歸僅僅提前做好互連本身框架性枝術,才行認為將差異裸片控制模塊資源共享在一件,造成某個巧妙的整體風格,認為改變更協調性的功能性、更厲害的性能方面,抗衡SoC單單片機芯片。

另,各個小基帶芯片推進封裝形式在在一塊后,高質量測試方法會稱為另一個凸起的方面,Intel也十分充分認識到在了這一些,會有效保證 使用整體高技術水平和全新方案設計,做好十分完正、深入淺出的測量查驗,另外在制成品揭曉后也會做好全八卦方位的測量,有效保證 獲得目標的質量和效能。這些年來的IC規劃設計中檢查確認開始越多越關鍵的,Intel會運用一點里面的專屬于的核實構思玩法,比較高有效率的地完工測驗方法儀步驟,相結行更開放的類產品核實,再者而且世上邊不能一點設計都可以需要滿足現在各種需求,還沒有里面的研發新的測驗方法儀機械設備, 以進一點挺高測驗方法儀核實有效率。

工作電壓,散熱處理一樣的是個要素點,Intel也是有合適的科技和存量,能很棒地徹底解決合并二極管裝封底邊裸片的熱區和共享wifi,一并還有單支切分科技,一并也會進兩步避免底邊裸片向頂部裸片的熱減壓反射,增強導熱性暴擊傷害。止于資金,能從辨癥的彎度去逛。這樣是把各個不一樣輸出模快合并二極管裝封在某個十分大的融合電路芯片內,硅資金是會提生,并且二極管裝封資金有很大的縮減了。這樣是把各個輸出模快都融合于某個小空間的SoCIC芯片上,硅總制造費行得以把握,然而 封裝類型分值和總制造費又大幅度加強。

匯總了:

在以前,看來沒有數量人關注度過封裝高技術,更想不上它談談末來每季度新品研發使用發展趨勢的關鍵的功用,Intel則能夠你預測性的眼觀、實力雄厚的技巧實力,向讓我們展出一堆個新款的全世界——之前,今后存儲芯片還也可以這個玩兒!

1立方米面,不一樣的的裝封技術性可能相互之間指向不一樣的的app供需,用在最切合的層級行業市場或是不祛除環保定制家具化設計。

另外一個管理方面,不相同的封口的技術也并不相互之間討厭,還能夠涉及性地樂隊組合在在一塊,克服新興供給,仿佛Co-EMIB就EMIB、Foveros融成的乙酰乙酸同樣。

在異構一體化的今天,成為四大技術性保障體系保障的Intel收獲無可厚非的壓到性優質,寄付就封裝的技術來說,Intel還有著一體化、全方面的消除措施。劃得來一提的是,然而哪些封裝形式技術設備措施均是Intel個性化的,尚未策劃一般開發授權管理,的Intel也在品嘗推動了封裝產業規則化的制定,從而就與三兩家產業培訓機構參與了之前接處。

半導體器件新新技術成長 到今日,摩爾定理都已經 難以能像民俗動向那么仍在神速向前,如果在六種新新技術柱石的土洞,Intel給予了摩爾熱力學定律新的代表什么意思,今后可期!